# 4K BIT (512 x 8)NVRAM

- · 4K Bit Static RAM backed by 4K Bit Electrically Erasable PROM

- Fully 5V Only Operation

- Directly TTL Compatible

- In Circuit EEPROM Changes

- SRAM Cycle Time less than 300 ns

- Power-Failure Protection

- Unlimited Recall Cycles

- Memory Margining Capability

- Operating ranges

52004 ..... 0°C to +70°C 520041.....-40°C to +85°C

52004HR..... -55°C to +125°C

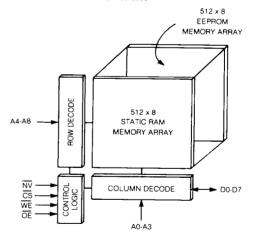

The NCR 52004 non-volatile RAM combines 4K (512 x 8) bits of conventional static RAM (SRAM) with an identical size array of Electrically Erasable PROM (EEPROM). Non-volatile data can be stored in the EEPROM while independent data is accessed simultaneously in the SRAM. Data can be transferred back and forth between the SRAM and the EEPROM by simple Store and Recall operations. A non-volatile Store signal transfers data from the SRAM to the non-volatile EEPROM where it is safely stored even when power is removed. When power is restored, the data in the EEPROM is automatically recalled into the SRAM. Data stored in the nonvolatile EEPROM can be recalled an unlimited number of times. The NCR 52004 requires only a single 5 volt power supply for all modes of operation, and is completely TTL compatible with fully static timing and three state outputs. The NCR 52004 is available in a 24 pin package and an optional 28 pin package, in commercial, industrial and high reliability versions.

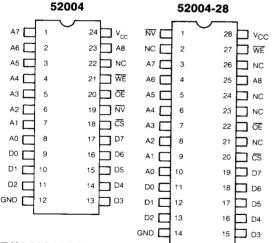

### PIN CONFIGURATION

### **FUNCTIONAL** BLOCK DIAGRAM

#### **PIN NAMES**

| A0-A8 | Address Inputs      | WĒ  | Write Enable   |

|-------|---------------------|-----|----------------|

| D0-D7 | Data I/0            | ŌĒ  | Output Enable  |

| ĊS    | Chip Select         | NC  | No Connection  |

| NV    | Non-Volatile Enable | Vcc | +5 Volts ± 10% |

Copyright © 1984 by NCR Corporation, Dayton, Ohio, U.S.A. All Rights Reserved. Printed in the U.S.A.

This is advance information and NCR reserves the right to change the specifications without notice.

# NCR

#### **DEVICE OPERATION**

#### **SRAM READ/WRITE**

The NCR 52004 can be read like a conventional static RAM. With  $\overline{CS}$  and  $\overline{OE}$  low and  $\overline{WE}$  high, valid data will be presented to output pins. With  $\overline{CS}$  and  $\overline{WE}$  low, and  $\overline{OE}$  high, the SRAM can be written to like a conventional static RAM.

#### **STORE**

Transferring data from the SRAM to the non-volatile EEPROM is controlled by the Store operation. The  $\overline{\text{NV}}$  input signal controls the non-volatile operations (i.e., Store and Recall), except for automatic data recall upon power up. When  $\overline{\text{NV}}$  and  $\overline{\text{WE}}$  are brought low, the entire contents of the SRAM array are copied into the non-volatile EEPROM array. The data in the SRAM is unaffected by a Store operation. The Recall cycle is inhibited by a Store operation, and  $\overline{\text{CS}}$  can either be high or low.

The I/O terminals are in the high impedance state during a Store operation. The contents of the EE-PROM remain valid with or without power being supplied. The data retention time of the EEPROM can be measured by memory margining.

During power up or power down, precaution must be taken to prevent an unintentional Store cycle. Holding NV high will inhibit the initiation of a Store cycle. Additionally, a Store operation should not be initiated until the supply voltage (VCC) is at specification limits.

#### RECALL

The data stored in the non-volatile EEPROM array is transferred back into the SRAM by the Recall operation. When  $\overline{\text{NV}}$  and  $\overline{\text{OE}}$  are brought low, the entire contents of the EEPROM are copied back into the SRAM (overwriting any data already existing in the SRAM). An Array Recall cycle can take place when  $\overline{\text{CS}}$  is either high or low. An array Recall operation will automatically be performed upon power up. The data in the EEPROM is unaffected by a Recall operation.

The Data I/0 terminals are in a high impedance state during a non-volatile operation (i.e., Store or Recall). When a non-volatile cycle is initiated, all other operations are inhibited until the first operation is complete.

#### **MEMORY MARGINING**

The NCR 52004 supports margining of the memory transistors. Memory margining allows device retention time to be projected for the purpose of device evaluation. An application note describing the memory margining algorithm is available.

#### MODE SELECTION

|        |    | INPUTS |    |    |  |  |  |  |  |  |  |  |

|--------|----|--------|----|----|--|--|--|--|--|--|--|--|

| MODE   | ĊŚ | N∇     | WE | ŌĒ |  |  |  |  |  |  |  |  |

| READ   | L  | Н      | Н  | L  |  |  |  |  |  |  |  |  |

| WRITE  | L  | Н      | L  | Н  |  |  |  |  |  |  |  |  |

| STORE  | Х  | L      | L  | Н  |  |  |  |  |  |  |  |  |

| RECALL | Х  | L      | Н  | L  |  |  |  |  |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

All inputs or outputs relative to Vss . . . . - 0.5 to + 7V Storage temperature without data retention . . . . . . . . -65°C to + 150°C

Stress above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operational limits stipulated elsewhere in this specification is not implied.

# RECOMMENDED OPERATING CONDITIONS

|        |                          | 52004 |     |     | 520041 |     |     | 52004HR ** |     |                 |      |

|--------|--------------------------|-------|-----|-----|--------|-----|-----|------------|-----|-----------------|------|

| Symbol | Parameter                | Min   | Тур | Max | Min    | Тур | Max | Min        | Тур | Max             | Unit |

| Vcc    | Supply voltage           | 4.5   | 5.0 | 5.5 | 4.5    | 5.0 | 5.5 | 4.5        | 5.0 | 5.5             | V    |

| VIH    | Input high level voltage | 2.0   |     | VCC | 2.0    | 0.0 | VCC | 2.0        | 5.0 | V <sub>CC</sub> | v    |

| VIL    | Input low level voltage  | -0.3  |     | 0.8 | -0.3   |     | 0.8 | -0.3       |     | 0.8             | v    |

| TA     | Ambient Temperature      | 0     |     | 70  | -40    |     | 85  | -55        |     | 125             | °C   |

All voltages are with respect to GND.

# STATIC ELECTRICAL CHARACTERISTICS, OVER RECOMMENDED OPERATION CONDITIONS (UNLESS OTHERWISE NOTED)

|                |                           | Ì                             |     | 52004 |     | İ   | 520041 |     |              | 52004HR | **  |            |

|----------------|---------------------------|-------------------------------|-----|-------|-----|-----|--------|-----|--------------|---------|-----|------------|

| Symbol         | Parameter                 | Condition                     | Min | Тур   | Max | Min | Тур    | Max | Min          | Тур     | Max | Unit       |

| IN             | Input leakage current     | V <sub>IN</sub> = 0V TO 5.5V  |     | 0.1   | 10  |     | 0.1    | 10  | <del> </del> | 0.1     | 10  | <u>μ</u> Α |

| Ю              | IO leakage current        | V <sub>O</sub> = 0.4V TO 5.5V |     | 0.1   | 10  |     | 0.1    | 10  |              | 0.1     | 10  | μA         |

|                |                           | Deselected                    |     |       |     |     |        |     |              |         |     |            |

| lcc            | Supply Current            | Outputs Open                  |     | 35    | 70  |     | 45     | 80  |              | 45      | 80  | mA         |

| Vон            | Output High Voltage       | I <sub>OH</sub> = −400µA      | 2.4 |       |     | 2.4 |        | l   | 2.4          |         | "   | v          |

| VOL            | Output Low Voltage        | lOL = 2.1mA                   |     |       | 0.4 |     | 1      | 0.4 |              |         |     | V          |

| T <sub>S</sub> | Non-Volatile storage time |                               | TBD |       |     | ļ   |        | 0.4 |              |         | 0.4 | V          |

<sup>\*</sup>Typical values are at 25°C and typical supply voltages.

# CAPACITANCE TA = 25°C, f = 1.0 MHz, VCC = 5V

|        |                                         |                             | <u> </u> | 52004 | _   | 1   | 520041 |     |     | 52004HR+ | -#x |      |

|--------|-----------------------------------------|-----------------------------|----------|-------|-----|-----|--------|-----|-----|----------|-----|------|

| Symbol | Parameter                               | Condition                   | Min      | Тур   | Max | Min | Тур*   | Max | Min | Тур      | Max | Unit |

| С      | Capacitance of Input<br>& Data I/O pins | All pins at<br>VSS (ground) |          |       | 10  |     |        | 10  |     |          | 10  | pF   |

<sup>\* \*</sup>The 52004HR Data is preliminary and is subject to change.

# AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS (UNLESS OTHERWISE NOTED)

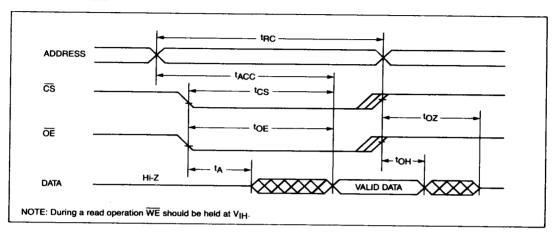

#### **READ CYCLE**

|                 |                                                               |     | 52004 |     |     | 520041 |     |     | 52004HR+ | *   |      |

|-----------------|---------------------------------------------------------------|-----|-------|-----|-----|--------|-----|-----|----------|-----|------|

| Symbol          | Parameter                                                     | Min | Тур   | Max | Min | Тур    | Max | Min | Тур      | Max | Unit |

| <sup>t</sup> RC | Read Cycle Time                                               | 300 |       |     | 300 |        |     | 450 |          |     | ns   |

| †ACC            | Address Access Time                                           |     |       | 300 |     |        | 300 |     |          | 450 | ns   |

| t <sub>A</sub>  | Chip Select or Output Enable to Data Active                   | 0   |       |     | 0   |        |     | 0   |          | ļ   | ns   |

| tOE             | Output Enable Time                                            |     |       | 100 |     |        | 120 |     |          | 120 | ns   |

| tcs             | Chip Select Access Time                                       |     |       | 100 |     |        | 120 |     |          | 120 | ns   |

| tOH             | Output Hold Time                                              | 10  |       | 1   | 10  |        |     | 10  | 1        |     | ns   |

| toz             | Chip Select Or Output Enable To Output<br>High Impedance Time |     |       | 90  |     |        | 90  |     |          | 90  | ns   |

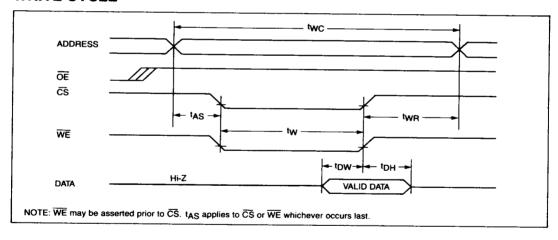

#### WRITE CYCLE

|                  |                            |     | 52004 |     |     | 520041 |     |     | 52004HR** |     |      |  |

|------------------|----------------------------|-----|-------|-----|-----|--------|-----|-----|-----------|-----|------|--|

| Symbol Parameter | Parameter                  | Min | Тур   | Max | Min | Тур    | Max | Min | Тур       | Max | Unit |  |

| twc              | Write Cycle Time           | 300 |       |     | 300 |        |     | 450 |           |     | ns   |  |

| tw               | Write Pulse Width          | 150 |       | 1   | 150 | ļ      |     | 300 |           |     | ns   |  |

| twr.             | Write Release Time         | 25  |       |     | 25  |        |     | 25  |           |     | ns   |  |

| tow              | Data to Write Time Overlap | 150 | İ     | İ   | 150 |        |     | 200 |           | '   | ns   |  |

| t <sub>DH</sub>  | Data Hold From Write Time  | 20  |       | }   | 20  |        |     | 20  |           |     | ns   |  |

| t <sub>AS</sub>  | Address Setup Time         | 50  | ŀ     |     | 50  |        |     | 50  |           |     | ns   |  |

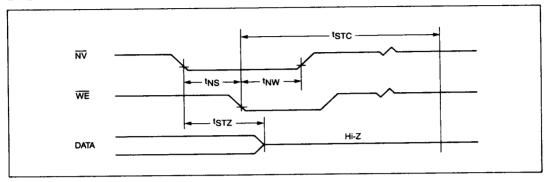

#### STORE CYCLE

| *******         |                        |     | 52004 |     |     | 520041 |     |     | 52004HR** |     |       |  |

|-----------------|------------------------|-----|-------|-----|-----|--------|-----|-----|-----------|-----|-------|--|

| Symbol          | Parameter              | Min | Тур   | Max | Min | Тур    | Max | Min | Тур       | Max | Unit  |  |

| tstc            | Store Cycle Time       |     |       | 10  |     |        | 10  |     |           | 10  | ms    |  |

| INW             | NV to Write Overlap    | 100 |       |     | 100 |        |     | 100 |           |     | ns    |  |

| <sup>t</sup> NS | NV Setup Time          | 0   |       | ĺ   | 0   |        |     | 0   |           |     | ns    |  |

| tSTZ            | Store to Output Hi-Z   |     |       | 100 |     |        | 100 |     |           | 100 | ns    |  |

| tsc             | Number of Store Cycles | 104 | ļ     |     | 104 | :      |     | 104 |           |     | cycle |  |

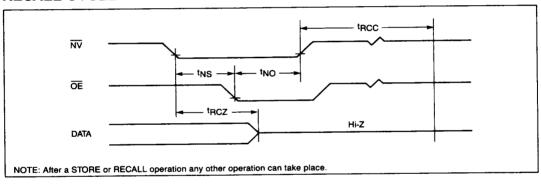

#### **RECALL CYCLE**

|                  |                         | 52004 |     | 520041 |     |          |     |     |     |     |      |

|------------------|-------------------------|-------|-----|--------|-----|----------|-----|-----|-----|-----|------|

| Symbol           | Parameter               | Min   | Тур | Max    | Min | Тур      | Max | Min | Тур | Max | Unit |

| <sup>t</sup> RCC | Array Recall Cycle Time |       |     | 20     |     |          |     |     | ]   |     | μS   |

| tNO              | NV to Output Overlap    | 200   |     |        | 450 |          |     | 450 |     |     | ns   |

| tNS              | NV Setup time           | 0     |     |        | 0   |          |     | 0   |     |     | ns   |

| <sup>†</sup> RCZ | Recall to Output Hi-Z   |       |     | 100    |     | <u> </u> | 100 |     |     | 100 | ns   |

<sup>\*\*</sup>The 52004HR Data is preliminary and is subject to change.

## **READ CYCLE**

## **WRITE CYCLE**

# NCR

## STORE CYCLE

## **RECALL CYCLE**

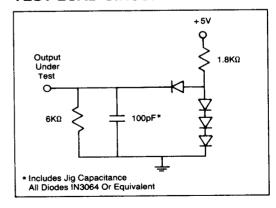

# A. C. CONDITIONS OF TESTS

| Input Pulse Levels      | 0.8 Volts to 2.0 Volts |

|-------------------------|------------------------|

| Input Rise & Fall Times | 10 nsec                |

| Output Timing Levels    | 0.8 Volts to 2.0 Volts |

# **TEST LOAD CIRCUIT**

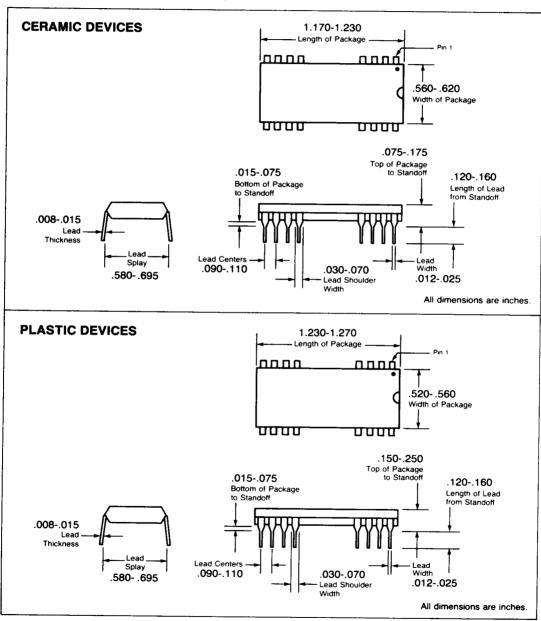

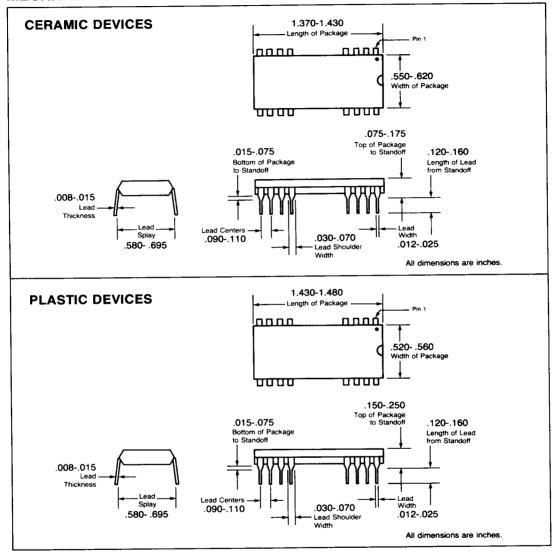

# MECHANICAL DATA 24 PIN

### MECHANICAL DATA 28 Pin

# NCR

NCR Microelectronics Division 8181 Byers Road Miamisburg, Ohio 45342

Telex: 241669 NCR NVMEM MSBG Phone: 1-800-543-5618 outside Ohio 513/866-7217 Ohio or International