# 8708

# 8192/4096 BIT ERASABLE AND ELECTRICALLY REPROGRAMMABLE READ ONLY MEMORY

### • 8708 1024x8 Organization

- Fast Programming Typ. 100 sec. For All 8K Bits

- Low Power During Programming

- Access Time 450 ns

- Standard Power Supplies— +12V, ±5V

- Static No Clocks Required

- Inputs and Outputs TTL Compatible During Both Read and Program Modes

- Three-State Output OR-Tie Capability

The Intel<sup>©</sup> 8708 is a high speed 8192 bit erasable and electrically reprogrammable ROM's (EPROM) ideally suited where fast turn around and pattern experimentation are important requirements.

The 8708 is packaged in a 24 pin dual-in-line package with transparent lid. The transparent lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written into the devices.

A pin for pin mask programmed ROM, the Intel $^{\odot}$  8308, is available for large volume production runs of systems initially using the 8708.

The 8708 is fabricated with the time proven N-channel silicon gate technology.

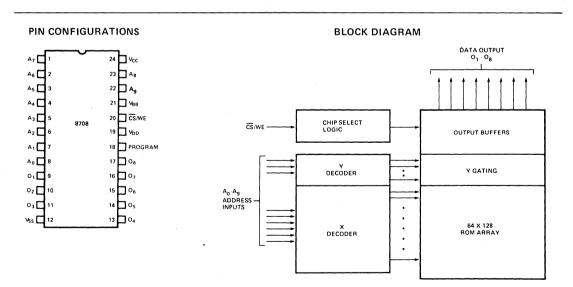

#### **PIN NAMES**

| A <sub>0</sub> ·A <sub>9</sub> | ADDRESS INPUTS                 |

|--------------------------------|--------------------------------|

| 01-08                          | DATA OUTPUTS                   |

| CS/WE                          | CHIP SELECT/WRITE ENABLE INPUT |

### **Absolute Maximum Ratings\***

| Temperature Under Bias                                                              | -25°C to +85°C |

|-------------------------------------------------------------------------------------|----------------|

| Storage Temperature                                                                 | 65°C to +125°C |

| All Input or Output Voltages with Respect to VBB                                    |                |

| (except Program)                                                                    | +15V to -0.3V  |

| Program Input to V <sub>BB</sub>                                                    | +35V to -0.3V  |

| Supply Voltages V <sub>CC</sub> and V <sub>SS</sub> with Respect to V <sub>BB</sub> | +15V to -0.3V  |

| V <sub>DD</sub> with Respect to V <sub>BB</sub>                                     | +20V to -0.3V  |

| Power Dissipation                                                                   | 1.5W           |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **READ OPERATION**

## **D.C.** and Operating Characteristics

$T_A = 0^{\circ} C$  to  $70^{\circ} C$ ,  $V_{CC} = +5 V \pm 5\%$ ,  $V_{DD} = +12 V \pm 5\%$ ,  $V_{BB} = -5 V \pm 5\%$ ,  $V_{SS} = 0 V$ , Unless Otherwise Noted.

| Symbol           | Parameter                                  | Min.            | Typ.[1] | Max.               | Unit | Conditions                                                              |

|------------------|--------------------------------------------|-----------------|---------|--------------------|------|-------------------------------------------------------------------------|

| ILI              | Address and Chip Select Input Load Current |                 |         | 10                 | μΑ   | V <sub>IN</sub> = 5.25V                                                 |

| ILO              | Output Leakage Current                     |                 |         | 10                 | μΑ   | V <sub>OUT</sub> = 5.25V, <del>CS</del> /WE = 5V                        |

| I <sub>DD</sub>  | V <sub>DD</sub> Supply Current             |                 | 50      | 65                 | mA   | Worst Case Supply Currents:                                             |

| lcc              | V <sub>CC</sub> Supply Current             |                 | 6       | 10                 | mA   | All Inputs High                                                         |

| I <sub>BB</sub>  | V <sub>BB</sub> Supply Current             |                 | 30      | 45                 | mΑ   | $\overline{\text{CS}}/\text{WE} = 5\text{V}; T_{A} = 0^{\circ}\text{C}$ |

| VIL              | Input Low Voltage                          | V <sub>SS</sub> |         | 0.65               | ٧    |                                                                         |

| V <sub>IH</sub>  | Input High Voltage                         | 3.0             |         | V <sub>CC</sub> +1 | ٧    |                                                                         |

| V <sub>OL</sub>  | Output Low Voltage                         |                 |         | 0.45               | ٧    | I <sub>OL</sub> = 1.6mA                                                 |

| V <sub>OH1</sub> | Output High Voltage                        | 3.7             |         |                    | >    | I <sub>OH</sub> = -100μA                                                |

| V <sub>OH2</sub> | Output High Voltage                        | 2.4             |         |                    | ٧    | I <sub>OH</sub> = -1mA                                                  |

| PD               | Power Dissipation                          |                 |         | 800                | mW   | T <sub>A</sub> = 70°C                                                   |

NOTES: 1. Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltages.

<sup>2.</sup> The program input (Pin 18) may be tied to VSS or VCC during the read mode.

# MCS-80

#### A.C. Characteristics

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = +5V \pm 5\%$ ,  $V_{DD} = +12V \pm 5\%$ ,  $V_{BB} = -5V \pm 5\%$ ,  $V_{SS} = 0V$ , Unless Otherwise Noted.

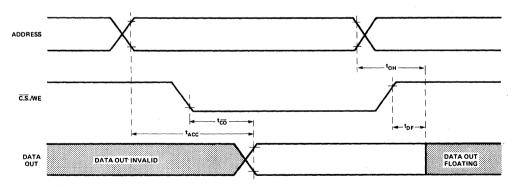

| Symbol          | Parameter                      | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------|------|------|------|------|

| tACC            | Address to Output Delay        |      | 280  | 450  | ns   |

| tco             | Chip Select to Output Delay    |      |      | 120  | ns   |

| t <sub>DF</sub> | Chip De-Select to Output Float | 0    |      | 120  | ns   |

| <sup>t</sup> он | Address to Output Hold         | 0    |      |      | ns   |

#### Capacitance<sup>[1]</sup> T<sub>A</sub> = 25°C, f = 1MHz

| Symbol           | Parameter          | Тур. | Max. | Unit | Conditions           |

|------------------|--------------------|------|------|------|----------------------|

| CIN              | Input Capacitance  | 4    | 6    | рF   | V <sub>IN</sub> =0V  |

| C <sub>OUT</sub> | Output Capacitance | 8    | 12   | pF   | V <sub>OUT</sub> =0V |

Note 1. This parameter is periodically sampled and not 100% tested.

#### A.C. Test Conditions:

Output Load: 1 TTL gate and  $C_L = 100 pF$

Input Rise and Fall Times: ≤20ns

Timing Measurement Reference Levels: 0.8V and 2.8V for inputs; 0.8V and 2.4V for outputs

Input Pulse Levels: 0.65V to 3.0V

#### Waveforms